Evolving a Better Branch Predictor

<

uArch-Directed Global Power Management

Hybrid CPU/GPU SAT Solver

A 1GHz Custom-Logic 16-bit DSP for Multimedia Applications

Profile-Directed Software Prefetching

Duchess: an Out-of-Order Alpha CPU

Autonomous Vehicle Navigation

Project Report (pdf)

Semester Project for Embedded System Design @ UT, Fall 2010

Semester Project for Embedded System Design @ UT, Fall 2010

- Methodology, language, and infrastructure to design branch predictors using genetic algorithms.

Project Report (pdf)

Semester Project for Multicore Computing @ UT, Spring 2010

Semester Project for Multicore Computing @ UT, Spring 2010

- DVFS GPM scheme, slows cores based off memory bottleneck % calculated using perf counters.

Project Report (pdf)

Semester Project for Comp Parallelism & Locality @ UT, Fall 2009

Semester Project for Comp Parallelism & Locality @ UT, Fall 2009

- Accelerated DPLL algorithm using CUDA. Used blocking, work stealing, 2.5x perf over baseline.

Project Report (pdf)

AMD Design Competition-Winning Semester Project for VLSI I @ UMich, Spring 2008

AMD Design Competition-Winning Semester Project for VLSI I @ UMich, Spring 2008

- 4-way SIMD, Sklansky adder, full custom datapath, clock gating, stream buffer, 7-stage pipeline, GShare.

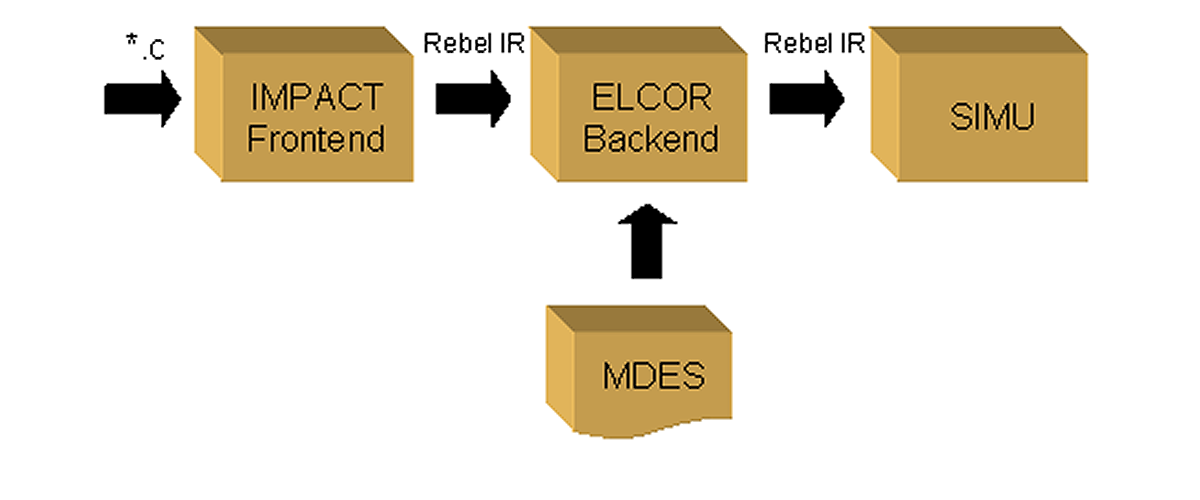

Semester Project for Back-end Compilers @ UMich, Fall 2007

- Profile info (stride, frequency, etc) used to insert prefetch instructions, written in C/C++ for Trimaran.

Project Report (pdf)

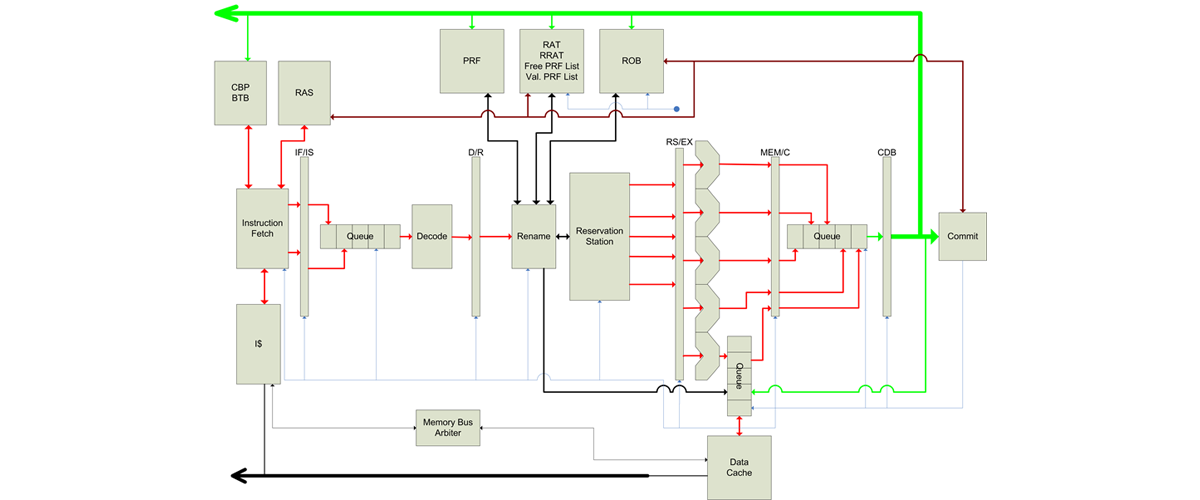

Semester Project for Computer Architecture @ UMich, Fall 2006

Semester Project for Computer Architecture @ UMich, Fall 2006

- Written with synthesizable Verilog, contains ROB, RRAT, RAS, GShare BP, OOO LSQ.

Project Report Website

Spring 2009 EECS373: Design of Microprocessor-based Systems

Spring 2009 EECS373: Design of Microprocessor-based Systems

- Modified a Power Wheels Barbie Jeep with a Freescale MPC555 microcontroller, steering mechanism, and IR/sonic sensors to support autonomous navigation.